# DESIGN AND INVESTIGATION OF A NEW PROTOCOL FOR A SINGLE WIRE LOW SPEED BI-DIRECTIONAL DATA BUS FOR EMBEDDED SYSTEMS

$\mathbf{BY}$

## Hasib Rahman 181-31-253

This Report Presented in Partial Fulfillment of the Requirements for the Degree of Bachelor of Science in Electronics and Telecommunication Engineering

Supervised By

Md. Taslim Arefin

Associate Professor & Head Department of ETE Daffodil International University

# DAFFODIL INTERNATIONAL UNIVERSITY DHAKA, BANGLADESH OCTOBAR 2019

#### **APPROVAL**

This Project titled "Design and investigation of a new protocol for a single wire low speed bidirectional data bus for embedded systems", submitted by Hasib Rahman to the Department of Electronics and Telecommunication Engineering, Daffodil International University, has been accepted as satisfactory for the partial fulfillment of the requirements for the degree of M.Sc. in Electronics and Telecommunication Engineering and approved as to its style and contents. The presentation was held on 27 October, 2019.

| <b>BOARD</b> | OF | EXA | MIN | <b>ERS</b> |

|--------------|----|-----|-----|------------|

|              |    |     |     |            |

(Md. Taslim Arefin)

Associate Professor & Head

Department of ETE

Faculty of Engineering

Daffodil International University

Chairman

Dr. M. Quamruzzaman)

Professor

Department of ETE

Faculty of Engineering

Daffodil International University

**Internal Examiner**

(tayer

(Dr. Md. Fayzur Rahman)

Professor & Chairperson

Department of EEE

Green University

**External Examiner**

#### **DECLARATION**

We hereby declare that, this project has been done by us under the supervision of **Md. Taslim** Arefin, Associate Professor & Head, Department of ETE, Daffodil International University. We also declare that neither this project nor any part of this project has been submitted elsewhere for award of any degree or diploma.

Supervised by:

Md. Taslim Arefin

**Associate Professor & Head**

**Department of ETE**

**Daffodil International University**

Submitted by:

Hasib Rahman

ID: 181-31-253

Department of ETE

Daffodil International University

#### **ACKNOWLEDGEMENT**

The very first words of acknowledgement deserve to be directed toward my thesis supervisor, Md. Taslim Arefin (Associate Professor & ETE dept. Head) for his valuable advice, guidance, constructive suggestions and making time from his busy schedule to advice and oversee my research work. I would like to offer him my profound indebtedness and sincere thanks along with my heartfelt gratitude.

I would like to thank and offer respect to all the authors of the application notes, research papers, journals, books and literature that were used throughout this research. The aforementioned materials not only helped my research but also broadened my reservoir of knowledge as well as my intellectual capacity.

And last but absolutely not least, I would like to offer a strong sense of gratitude to this intensely powerful supercomputer that I was able to use throughout, not only this research, but literally my whole life. Honestly, without it, it would have been literally impossible to complete this research, to achieve my M.Sc. in ETE, my B.Sc. in EEE, to learn, understand and apply science in my daily life and the list goes on. Therefore, a fairly large piece of this acknowledgement note is reserved for this approx. 1400 grams of various types of biological cells that comes together to form this supercomputer which is physically suspended in cerebrospinal fluid and physically resides inside my head.

#### **ABSTRACT**

A new protocol for a low speed single wire half duplex serial digital data BUS utilizing Master-Slave configuration is proposed in this thesis. Industry standard single wire data BUS already exists in the market from multiple large name brands. These existing single wire protocols work by either using delay based digital logic state definition or Manchester encoding or some other encoding technique to multiplex both data and clock in the same transmitted bit. Existing data buses generally have a standard speed of around 15Kbps and around 100kbps at high speed or overdrive mode. The data is kept synchronous by syncing with falling or rising edge of the transmitted signal.

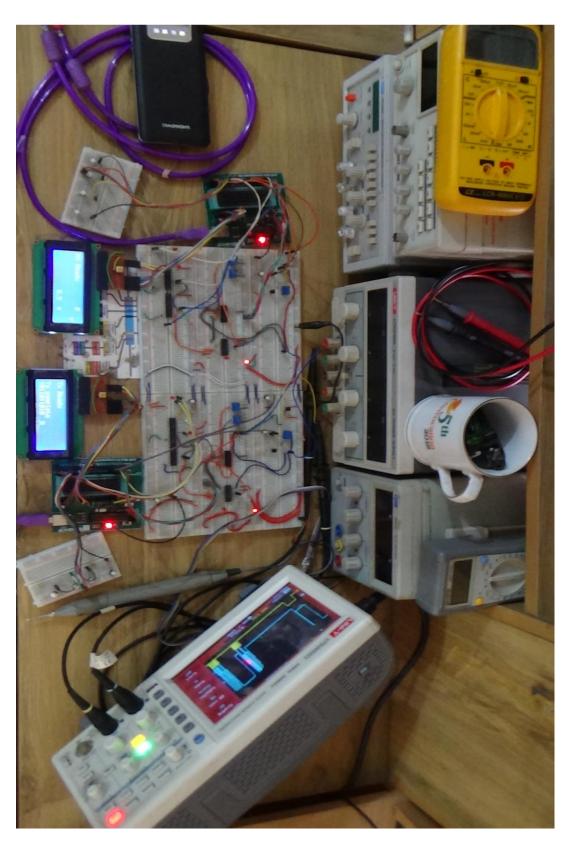

The proposed data BUS tries to multiplex data and clock in an unconventional way. An existing standard for digital logic state definition has been slightly modified to suit the requirements. In the research, attempts are made to combine both a digital data and an analog Clock signal on the transmitter side and separate the clock and digital data on the receiver side. The hardware for the combining and separating signals are designed to be as simple as possible. The whole system is tested out on a breadboard prototype using off the shelf components. Prototype consists of the individual transmitting and receiving modules and their respective Microcontroller Unit(s) running respective behavior model programs to simulate a functional transmitter and receiver, that are communicating predefined data at real time. Prior to construction of the prototype, detailed computer simulation has been generated to observe to viability of the idea, to test the designed circuits and to find and fix the bugs and signal glitches. Computer simulation is kept limited between voltage sweep and interactive simulation depending on the circuit and the virtual test instruments made available by the said simulator.

Although signal degradation occurred in the prototype, which was not present in the computer simulation, the BUS behaved exactly as predicted. Results from both the simulations and hardware prototype shows that it is possible to communicate in the proposed manner. The result from the proposed Single Wire data BUS is compared to the existing protocols to reveal that it is possible to theoretically exceed (21Kbps to 27Kbps) the standard speed of the existing protocols even with the breadboard implementation of the proposed data BUS.

## TABLE OF CONTENT

| CONTENTS                   |                                                                                                                                                | Page<br>No                 |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Board of examine           | ers                                                                                                                                            | ii                         |

| Declaration                |                                                                                                                                                | iii                        |

| Acknowledgeme              | nts                                                                                                                                            | iv                         |

| Abstract                   |                                                                                                                                                | v                          |

| Table of Content           |                                                                                                                                                | vi – vii                   |

| List of Figures            |                                                                                                                                                | viii – xi                  |

| List of tables             |                                                                                                                                                | xii                        |

| CHAPTER                    |                                                                                                                                                |                            |

| Chapter: 1 1.1 1.2 1.3     | Introduction Objective of this thesis work Possible Outcome Organization of the thesis                                                         | 1<br>2<br>2<br>3           |

| 2.1<br>2.2<br>2.3<br>2.4   | Digital data Communication BUS Parallel data BUS Serial Data BUS Comparison between Serial and Parallel BUS Effects of noise and attenuation   | 5<br>5<br>6<br>7<br>8      |

| 3.1<br>3.2<br>3.3<br>3.4   | Common protocols for 8-bit serial communication I2C/IIC Working principle of IIC Serial Protocol (EIA/TIA 232) Requirement for single wire BUS | 11<br>11<br>12<br>14<br>16 |

| <b>Chapter : 4</b> 4.1 4.2 | Existing single wire BUS protocols 1-Wire Protocol UNI/O                                                                                       | 18<br>18<br>23             |

| Chapter: 5 | Proposed Single Wire BUS                                | 26 |

|------------|---------------------------------------------------------|----|

| 5.1        | Working principle                                       | 26 |

| 5.2        | Data frame format, BUS modes and communication protocol | 29 |

| 5.2.1      | Data frame format                                       | 30 |

| 5.2.2      | BUS modes                                               | 30 |

| 5.2.3      | Communication protocol                                  | 31 |

| 5.3        | M-Ary modulation and buffering                          | 32 |

| 5.4        | System and sub-system block diagrams                    | 33 |

| 5.4.1      | Multiplexer                                             | 34 |

| 5.4.2      | Timer                                                   | 34 |

| 5.4.3      | Isolator                                                | 36 |

| 5.4.4      | Error handler                                           | 38 |

| 5.5        | Complete protocol                                       | 40 |

| Chapter: 6 | Hardware Design                                         | 41 |

| 6.1        | Signal Multiplexer                                      | 41 |

| 6.2        | Multiplexer working principle                           | 42 |

| 6.3        | Isolator                                                | 46 |

| 6.4        | Isolator working principle                              | 48 |

| 6.5        | Test Setup of complete module                           | 51 |

| 6.6        | Transmitter and receiver behavior model                 | 57 |

| 6.6.1      | Transmitter                                             | 57 |

| 6.6.2      | Receiver                                                | 59 |

| Chapter: 7 | <b>Experimental Hardware Emulation and Results</b>      | 61 |

| 7.1        | Experimental Setup result                               | 63 |

| Chapter: 8 | Conclusion                                              | 71 |

| 8.1        | Thesis Summary                                          | 72 |

| 8.2        | Present problems solved by the proposed data BUS        | 73 |

| 8.3        | Probable future development(s)                          | 74 |

| References |                                                         | 76 |

| Appendix   |                                                         | 78 |

| A          | List of abbreviations                                   | 78 |

| В          | List of Designators used in the Schematic               | 79 |

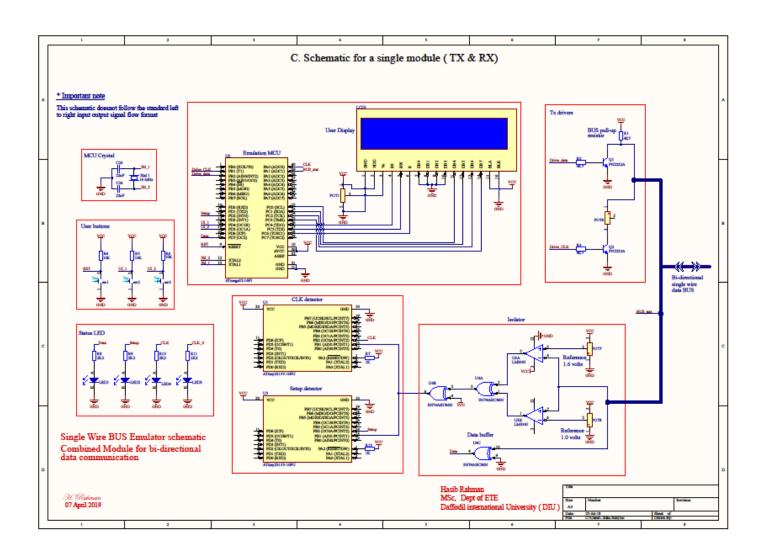

| C          | Schematic for hardware emulation                        | 80 |

| D          | Emulation hardware setup                                | 81 |

## LIST OF FIGURES

| FIGURES     |                                                                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.1  | IIC timing diagram for sending Address followed by data                                                                                  |

| Figure 3.2  | Devices and pull-up resistor connection of a typical IIC BUS                                                                             |

| Figure 3.3  | Single ended transmission with line noise and ground noise model                                                                         |

| Figure 3.4  | Differential transmission with line noise and ground noise model                                                                         |

| Figure 3.5  | Data frame format of TIA/EIA 232 standard                                                                                                |

| Figure 4.1  | Typical device connections of 1-wire protocol                                                                                            |

| Figure 4.2  | Typical communication flow of 1-wire protocol                                                                                            |

| Figure 4.3  | 1-wire protocol reset with at least 1 slave                                                                                              |

| Figure 4.4  | 1-wire reset with no slave                                                                                                               |

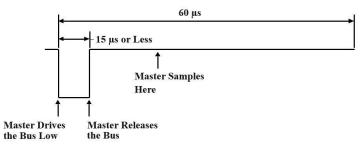

| Figure 4.5  | 1-wire Write 0 (digital LOW)                                                                                                             |

| Figure 4.6  | 1-wire Write 1 (digital HIGH)                                                                                                            |

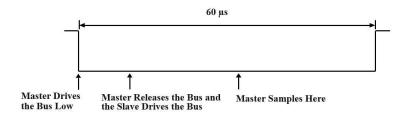

| Figure 4.7  | 1-wire Read 1 (digital HIGH)                                                                                                             |

| Figure 4.8  | 1-wire Read 0 (digital LOW)                                                                                                              |

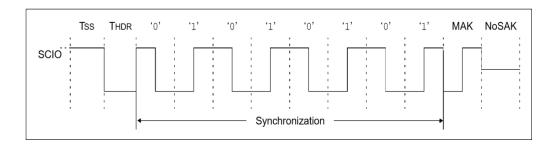

| Figure 4.9  | UNI/O BUS example                                                                                                                        |

| Figure 4.10 | Manchester encoding                                                                                                                      |

| Figure 4.11 | UNI/O one-byte transmission using Manchester Encoding                                                                                    |

| Figure 4.12 | UNI/O complete one-byte transmission with both Master and Slave acknowledgement                                                          |

| Figure 4.13 | Complete timing diagram for read operation from UNI/O compatible EEPROM                                                                  |

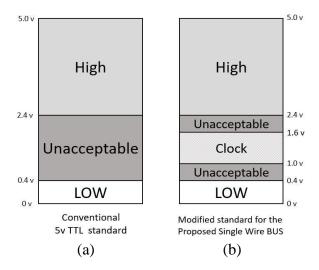

| Figure 5.1  | Figure 5.1 Voltage Levels for the logic states  (a) Conventional 5v TTL standard, (b) Modified standard for the proposed single wire BUS |

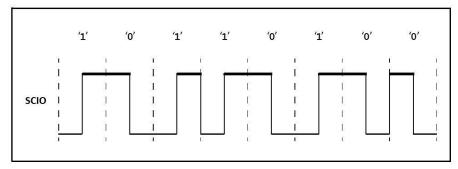

| Figure 5.2               | Digital signal waveform for conventional TTL standard                                                                           |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.3<br>Figure 5.4 | Digital signal waveform for proposed single wire standard Data frame for the proposed single wire standard                      |

| Figure 5.5               | M-ary modulation of binary data                                                                                                 |

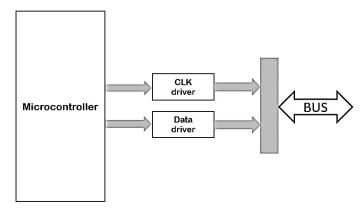

| Figure 5.6               | Block diagram of data and clock multiplexing circuit                                                                            |

| Figure 5.7               | Block diagram of clock isolating circuit (isolator)                                                                             |

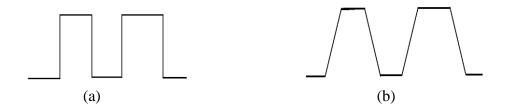

| Figure 5.8               | Figure 5.7 Voltage transition (a) Digital signal, (b) Actual continuous representation of voltage transition                    |

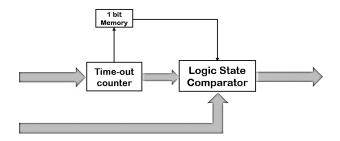

| Figure 5.9               | Block diagram of clock detection circuit (subsystem of isolator)                                                                |

| Figure 5.10              | Block diagram of combined multiplexer and demultiplexer to form a single module                                                 |

| Figure 5.11              | Block diagram of BUS latch up prevention circuit (error handler)                                                                |

| Figure 5.12              | Complete block diagram of combined multiplexer and demultiplexer to form a single module                                        |

| Figure 6.1               | Resistive voltage divider  (a) Clock voltage level generator, (b) Data voltage level generator                                  |

| Figure 6.2               | Clock generating circuit                                                                                                        |

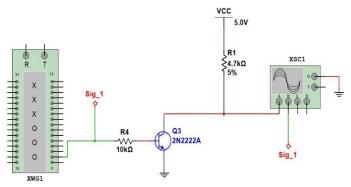

| Figure 6.3               | Data generating circuit                                                                                                         |

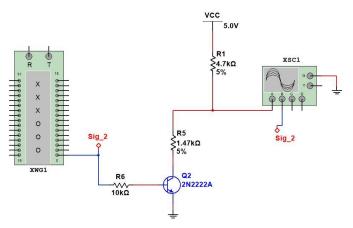

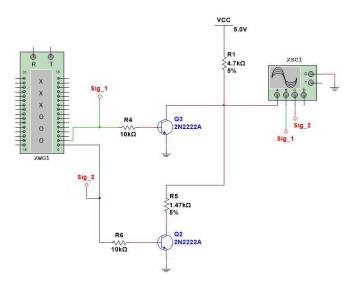

| Figure 6.4               | Complete multiplexing circuit                                                                                                   |

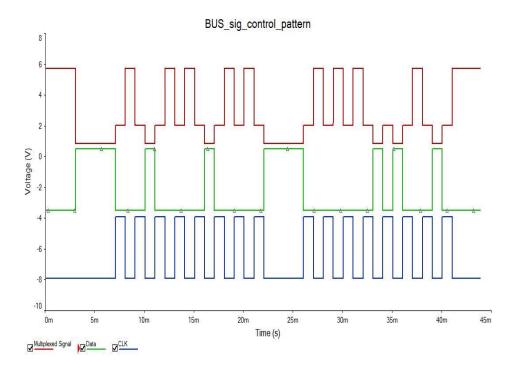

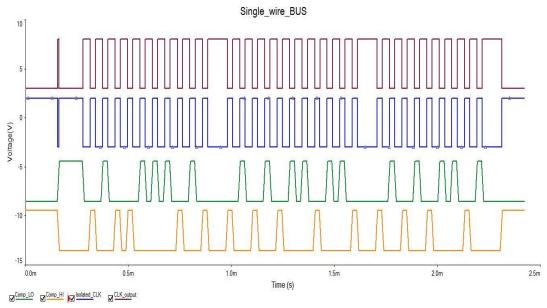

| Figure 6.5               | Timing diagram and output of the multiplexing circuit<br>From bottom to top: CLK (blue), Data (green), Multiplexed signal (red) |

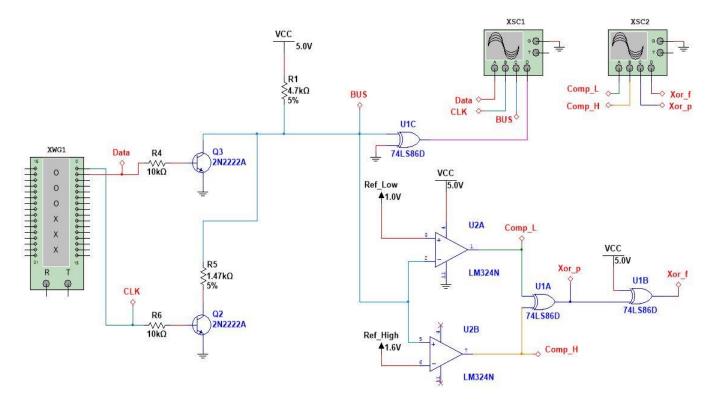

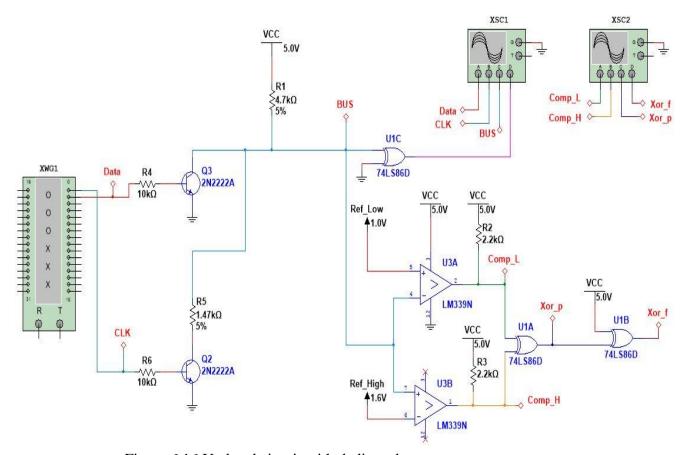

| Figure 6.6               | Complete isolator circuit                                                                                                       |

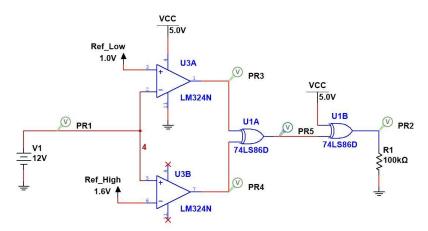

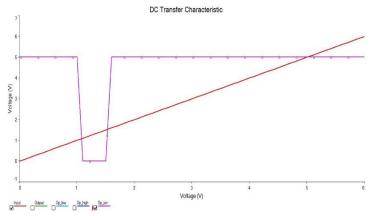

| Figure 6.7               | DC sweep of the isolator                                                                                                        |

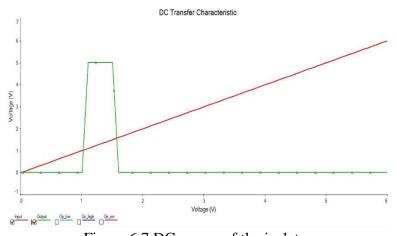

| Figure 6.8               | DC sweep of low threshold comparator                                                                                            |

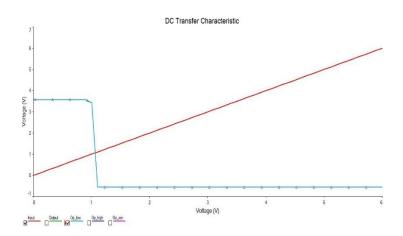

| Figure 6.9               | DC sweep of high threshold comparator                                                                                           |

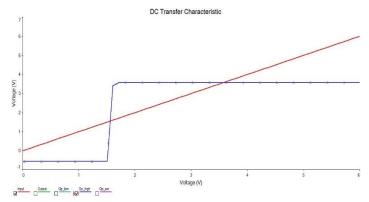

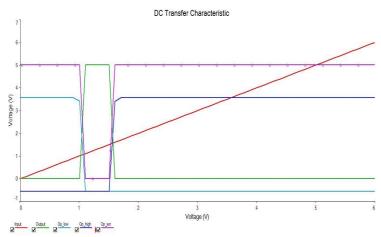

| Figure 6.10 | DC sweep of comparator XOR gate                                                                                                                                        |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.11 | DC sweep of all components of the isolator                                                                                                                             |

| Figure 6.12 | Complete circuit combining TX RX module                                                                                                                                |

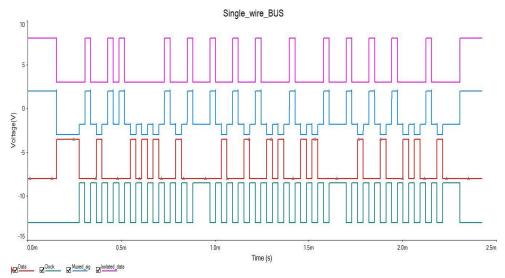

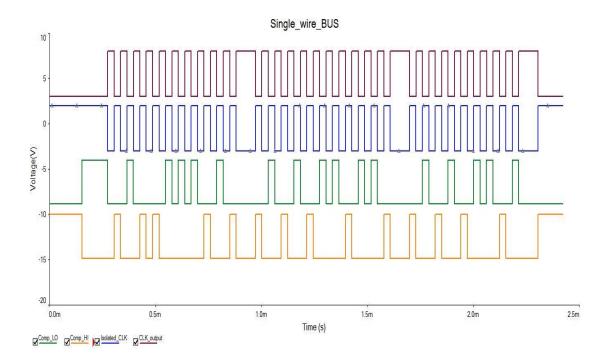

| Figure 6.13 | Waveform of the combined module<br>From bottom to top: CLK, Data, Multiplexed signal and extracted data from<br>multiplexed signal                                     |

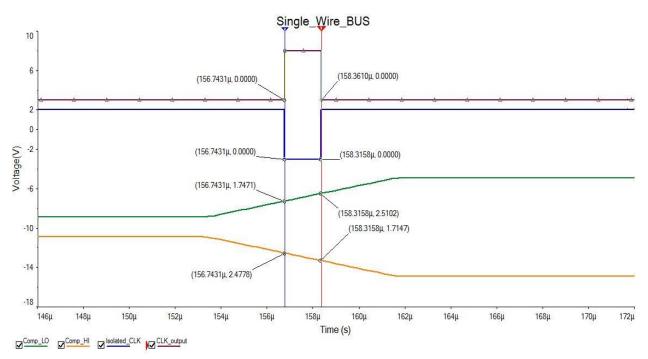

| Figure 6.14 | Waveform of the isolator output<br>From bottom to top: Output of high and low Comparator, XOR gate U1A and<br>extracted CLK from multiplexed signal                    |

| Figure 6.15 | Glitch in the isolator due to slow slew rate of the op-amps                                                                                                            |

| Figure 6.16 | Updated circuit with dedicated comparator op-amps                                                                                                                      |

| Figure 6.17 | Waveform of the updated circuit<br>From bottom to top: Output of high and low Comparator, XOR gate U1A and<br>extracted CLK from multiplexed signal                    |

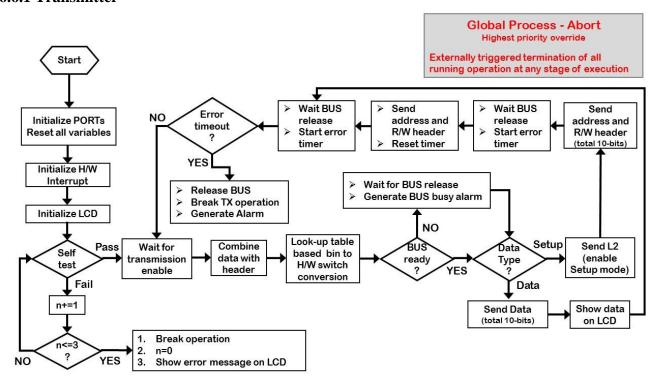

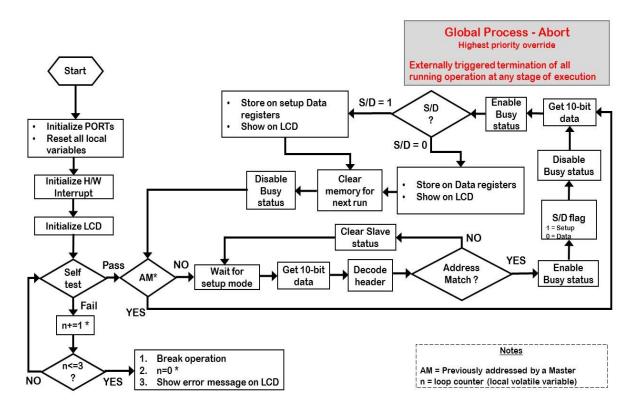

| Figure 6.18 | Transmitter behavioral model flow diagram                                                                                                                              |

| Figure 6.19 | Receiver behavioral model flow diagram                                                                                                                                 |

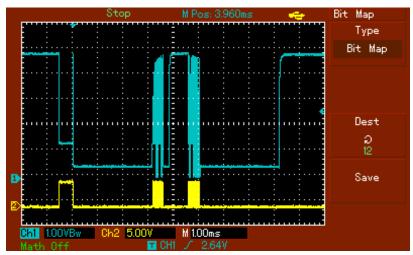

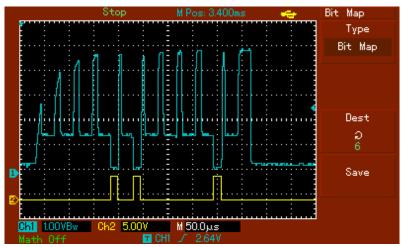

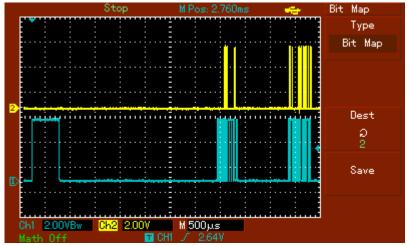

| Figure 7.1  | Initialization of setup mode followed by transmission of slave address and one data packet (BUS & CLK, blue and yellow respectively)                                   |

| Figure 7.2  | Initialization of setup mode followed by transmission of slave address and one data packet (BUS & data, blue and yellow respectively)                                  |

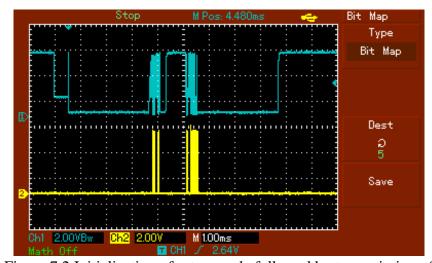

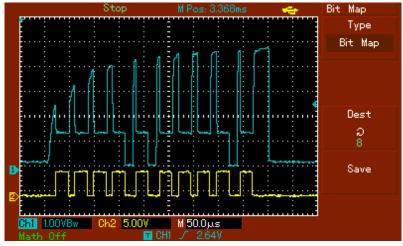

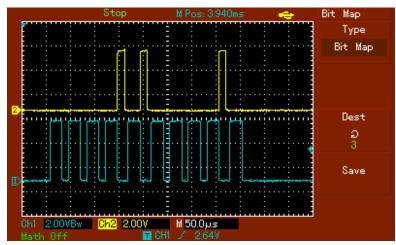

| Figure 7.3  | Transmission of address and header (BUS & CLK, blue and yellow respectively)                                                                                           |

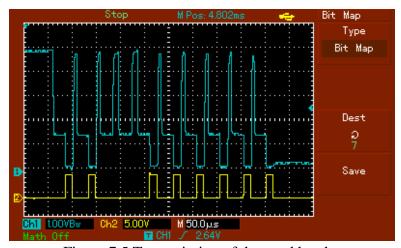

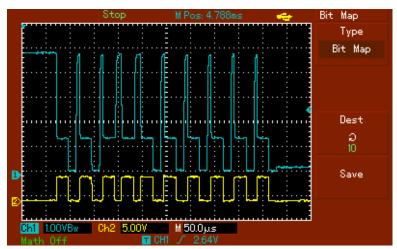

| Figure 7.4  | Transmission of data and header (BUS & CLK, blue and yellow respectively)                                                                                              |

| Figure 7.5  | Transmission of data and header (BUS & data, blue and yellow respectively)                                                                                             |

| Figure 7.6  | Transmission of data and header (BUS & data, blue and yellow respectively)                                                                                             |

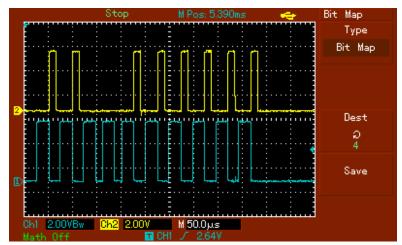

| Figure 7.7  | Transistor switching pattern for initialization of setup mode followed by transmission of slave address and one data packet (data & CLK, yellow and blue respectively) |

| Figure 7.8 | Transistor switching pattern for transmission of slave address and command header (data & CLK, yellow and blue respectively) |

|------------|------------------------------------------------------------------------------------------------------------------------------|

| Figure 7.9 | Transistor switching pattern for transmission of data and command header (data & CLK, yellow and blue respectively)          |

| Figure 8.1 | Signal level transition                                                                                                      |

## LIST OF TABLES

| Table 2.1 | Pinout of Parallel-ATA (PATA) BUS                                                              |

|-----------|------------------------------------------------------------------------------------------------|

| Table 2.2 | Pinout of Serial-ATA (SATA) BUS                                                                |

| Table 2.3 | Comparison between Serial and Parallel BUS                                                     |

| Table 3.1 | comparison between IIC and TIA/EIA 232                                                         |

| Table 5.1 | Command headers and their respective mode descriptions                                         |

| Table 6.1 | Component list for multiplexing circuit                                                        |

| Table 6.2 | Component list for isolator circuit                                                            |

| Table 6.3 | Component list for complete module circuit                                                     |

| Table 7.1 | Component list for protoboard hardware emulator                                                |

| Table 7.2 | List of instruments, simulation package and CAD packages used in the research                  |

| Table 7.3 | Comparison between existing industry standard single wire BUS against proposed single wire BUS |

## Chapter – 1

#### Introduction

Modern civilization is heavily dependent on electronic technologies. With improvement of electronic technologies, devices are becoming more capable, efficient, smarter and smaller. An individual standalone electronic system is now capable of working in conjecture with other individual standalone system(s) to offer a better and more efficient way of solving any particular task no matter the complexity. To work in conjecture with one another, the devices/systems need to communicate between each other. In order for the standalone systems to communicate between each other, a common communication medium and a common communication protocol is necessary. There exist multiple different kinds of communication protocols each with its own characteristics, advantages, disadvantages, operating conditions and limitations. Communication between standalone systems can be achieved via wired, wireless or optical medium. This thesis paper focuses on communication BUS and protocols used by embedded systems using wired medium.

In the thesis paper, a new single wire digital data BUS is proposed. The data BUS is implemented using a new/experimental signaling protocol that multiplexes digital data and clock signal in to a single signal. The signaling protocol can be thought of as a cross between the traditional 5v TTL standard and an analog pulsating dc signal. In the traditional 5v TTL standard, the threshold for logical HIGH is set for voltages that are greater than or equal to 2.4v. The logical LOW is set for less than or equal to 0.4v. The middle section between 0.4v to 2.4v is left unused. Any electrical pulse in this region is regarded by a digital logic circuit as undefined (metastable state) and is discarded. In this thesis, circuits and protocols are generated that allows usage of the undefined region to carry the clock signal without disturbing/affecting the digital data. Circuits are designed to combine both the digital data and digital clock signal, transmit them and at the receiving end, receive and separate them to retrieve the sent digital data.

There are multiple commercially available single wire BUS in the market, however, none of them uses this specific signaling method and protocol researched in this thesis work. The proposed BUS uses single ended signaling to carry data and CLK.

#### 1.1 Objective of this thesis work

The objective of this thesis work is to

- Research a new way to communicate data between multiple chip/devices/systems using only single physical wire utilizing the proposed signaling protocol

- Design and simulate the hardware for the BUS on a PC based simulator

- Build a hardware prototype to verify the designed BUS in real time in real life scenario

- Compare and contrast to existing technology(s)

#### 1.2 Possible Outcome

The main section of the proposed single wire data BUS is its ability to multiplex digital data and clock signal. The following outcomes are expected

- The multiplexing/encoding circuit will generate a completely new signal waveform with provided clock and data

- The demultiplexing/decoding circuit will extract both the clock and data signal from the newly generated signal, transmitted through a single physical wire

- The protocol is expected to have a lossless exchange of synchronous data at bit rate of at least 10 Kbits/s (theoretically)

#### 1.3 Organization of the thesis

This thesis work deals with serial data BUS, and therefore, a brief overview of serial and parallel data BUS is provided to justify the popularity of serial BUS. The proposed BUS is intended to be used with embedded systems. To justify the necessity for a single wire BUS, some very popular multi wire data BUS are discussed briefly. The result of the proposed single wire digital data BUS is compared to existing single wire BUS later in the thesis report and therefore, existing single wire data BUS is also explained briefly. The thesis report is organized as follows

Chapter 1 – The introductory chapter that set the aim and motivation behind this thesis research. It also defines the objective and predicts the outcome of the research.

Chapter 2 – Provides a brief overview of two different ways digital data is exchanged via wired medium, compares them from different practical aspects and points out why serial protocols are preferred over parallel protocols in modern embedded systems.

Chapter 3 – Briefly describes the working principle and limitations of two of the most widely used serial data BUS for embedded systems and tries to justify the requirement for single wire data BUS.

Chapter 4 – Gives a light overview of the existing industry standard single wire data BUS, describes their working principle, applications, advantages, disadvantages and limitations. This chapter is presented here so that it can be later referred to when comparing the proposed single wire data BUS to the existing ones.

Chapter 5 – Describes the proposed single wire data BUS, its working principle, block diagram and the functionality of the blocks.

Chapter 6 – Deals with the design and working principle of the circuits to multiplex and demultiplex the digital data and clock signal, show and discuss the results of the simulation

waveforms and discuss the behavior models for a dummy transmitter and receiver to communicate data using the proposed single wire BUS in real time.

Chapter 7 – Presents and discusses the results of bread board prototype.

Chapter 8 – Concluding remark of this thesis work along with summary and probable research topics to update this proposed data BUS in future.

Reference – Chapter 8 is followed by reference containing detail information of all the documents, books and literatures used in the research and in this thesis paper.

Appendix – Consists of two sections namely A and B. Section A contains list of abbreviations used throughout this literature and section B contains list of designators used in the schematic of the actual electronic circuit generated by CAD tool.

## Chapter – 2

## **Digital Data Communication BUS**

Any digital system can transfer data either serially or in parallel using serial communication or parallel communication method respectively. In both case for higher degree of accuracy and efficiency, data synchronization signal is needed. The synchronization signal is generally referred to as Clock signal and the frequency of the Clock signal is termed as Clock speed. Higher the Clock speed of the data BUS, faster is the data transmission rate. Note that this thesis is inclined toward microcontroller based systems and therefore only the BUS that are commonly used by 8-bit MCU are considered here. A very brief overview of both parallel and serial communication is provided in section 2.1 and section 2.2.

#### 2.1 Parallel data BUS

Parallel data BUS uses multiple data line to communicate data. Ideally, the number of parallel data lines equals number of bits on the data e.g. a simple ideal 8-bit parallel data BUS will have 8 data lines. In reality the number of parallel data lines will be higher as Clock signal, various control signals, status and/or acknowledgement signals are also communicated through the BUS. To transmit data in simplest form (without control, status and acknowledgment signals) through an 8-bit parallel BUS, the 8-bit data is placed on 8-bit data BUS (1 bit per line making sure to place LSB and MSB in their respective position on the BUS) and the Clock signal is transmitted by the transmitter. Once the receiver receives the Clock signal, it takes in the bits that are in the parallel data lines. The process is repeated each time data needs to be transferred. Parallel data BUS therefore, physically, consists of a large number individual wires on the data BUS and requires a large number of physical pins on the IC/system handling the data, both on transmitter and receiver, that is using the said BUS.

Table 2.1 shows the pinout of Parallel ATA (PATA) BUS conventionally used by computers to connect motherboard to external devices such as hard disk, floppy drive, CD-ROM drive etc. A 40

pin connector, connected to 40 pin ribbon cable, would be used to physically connect the 40 pin BUS to the motherboard and other devices. Note that of the 40 pin connector, only 16 pins are used to convey data. Rest are different control signals address, chip select, ACK etc.

| Signal         | Pin number | Pin number | Signal         |

|----------------|------------|------------|----------------|

| GND            | 2          | 1          | RST            |

| DD8            | 4          | 3          | DD7            |

| DD9            | 6          | 5          | DD6            |

| DD10           | 8          | 7          | DD5            |

| DD11           | 10         | 9          | DD4            |

| DD12           | 12         | 11         | DD3            |

| DD13           | 14         | 13         | DD2            |

| DD14           | 16         | 15         | DD1            |

| DD15           | 18         | 17         | DD0            |

| VCC in         | 20         | 19         | GND            |

| GND            | 22         | 21         | DDRQ           |

| GND            | 24         | 23         | I/O W          |

| GND            | 26         | 25         | I/O R          |

| CS             | 28         | 27         | IOCHRDY        |

| GND            | 30         | 29         | DDACK          |

| N/C            | 32         | 31         | IRQ            |

| DMA66 detect   | 34         | 33         | ADDR 1         |

| ADDR 2         | 36         | 35         | ADDR 0         |

| Chip select 3P | 38         | 37         | Chip select 1P |

| GND            | 40         | 39         | Activity       |

Table 2.1 Pinout of Parallel-ATA (PATA) BUS

#### 2.2 Serial Data BUS

Serial data BUS uses much lower number of wires to communicate data. Common serial data BUS like IIC or SPI uses one or two wire to send/receive data and a single dedicated wire for transmitting Clock signal. In a simple ideal 8-bit serial data BUS, the 8-bit data is first placed serially on the data wire/line and then Clock signal is applied. Each CLK sends one-bit serial data. Therefore, for an 8bit data, 8 CLK are needed to completely transmit it. However unlike parallel BUS, where the number of wires can increase depending on control, status and acknowledge signals, the number of wires on serial BUS can stay same. The control, status and acknowledge

bits can be serially sent using the same wires that are used to send data, however, more CLK are then needed. E.g. if there are 1 control bit, 1 status bit and 1 acknowledge bit on an 8bit serial data BUS, a total of 8+3 = 11 CLK are needed to transmit the whole data. Therefore, serial data BUS requires significantly less number of physical pins on the IC/system handling the data, both on transmitter and receiver, that is using the said BUS. This makes serial BUS very popular in digital systems.

Table 2.2 shows the pinout of a Serial ATA (SATA) data BUS. Note the reduction of pin numbers from 40 pin to 7 pins. Unlike PATA, SATA uses differential pairs to convey signals, one pair for the receiver (B+ & B-) and another pair for the transmitter (A+ & A-).

| Pin number | Signal                                                |  |

|------------|-------------------------------------------------------|--|

| 1          | Ground                                                |  |

| 2          | A+ (transmit)                                         |  |

| 3          | A- (transmit)                                         |  |

| 4          | Ground                                                |  |

| 5          | B- (receive)                                          |  |

| 6          | B+ (receive)                                          |  |

| 7          | Ground                                                |  |

| 8          | Coding notch (nonconductive, built on the connectors) |  |

Table 2.2 Pinout of Serial-ATA (SATA) BUS

#### 2.3 Comparison between Serial and Parallel BUS

In parallel data BUS, a lot of physical wires are used to transfer one or more bytes at a time. A lot of data can be transferred in a very short time in this way. A serial data BUS requires significantly lower number of physical wires, however, requires a significantly higher number of Clock signals. This is a tradeoff between physical wires vs communication speed. In the early days of computer, the technology to generate, control high clock speed and handle high data transmission was not available (even if the technology existed, it was too expensive and was financially impractical) and so parallel BUS was very popular e.g. Intel i51, i85, i86 and Pentium series processors used 8/16/32/64-bit parallel BUS for data and address. As technology improved, high speed data handling capability has also been developed (and fabrication price is reduced significantly) resulting in serial data BUS that are orders of magnitude faster than conventional

parallel data BUS. It is true that using the same technology, parallel systems can also be made faster, however, parallel BUS requires a large number of physical connections which are not practical by today's standard, at least in case of system design (VLSI design frequently uses combination of serial and parallel BUS). Furthermore, effect of noise and signal attenuation must also be considered which are explained in the next section.

#### 2.4 Effects of noise and attenuation

Every piece of current carrying wire, by nature, has properties to acts like an antenna. In principle, an antenna can both receive and transmit signals. Therefore, every physical wires, carrying digital/analog signal, will always act like an antenna and will both radiate and receive signals in the appropriate range of the EM spectrum.

Fourier analysis of radiating signals will point out that the emitted/radiated frequency includes the fundamental frequency (frequency of original signal carried by the conductor) and several harmonics of the fundamental frequency. All of these emitted signals are not an intended part of the original design and are therefore considered to be noise. Furthermore, signals emitted by one wire can be picked up by another wire carrying different signal as all wires can act like antenna. These picked up stray signals or noise can interact with the original signals and, in worst case, may cause change in logic state of the original signal. The noise can get out of the actual system that generates it and spread out on the surrounding environment. If the system is generating the noise, the noise is labeled as Electromagnetic Interference (EMI). If the system is picking up the noise, the noise is known as Electromagnetic Crosstalk (EMC). EMI/EMC can destabilize sensitive digital systems (e.g. high speed telecom or RF instrument, computers, audio-video systems etc.), make systems such as analog acquisition circuits to acquire wrong data and may cause false state switching of CMOS circuit(s). Any form of electromagnetic radiation can also affect biological and ecological systems (affect depends on frequency and power of the signal). Electromagnetic radiation (radiated emission) can also escape its source via power line (conducted emission) and may destabilize electronic system (causing fire in worst case) connected to the same power BUS. This is the reason why developed countries has a strong set of guidelines for allowed EMI, RFI level for all the electronic products that enters the said country legally, for example, USA has FCC

standard, EU has CE standard, Japan has VCCI and all developed countries, will most probably, accept UL (Universal Listing) standard(s). There are separate guidelines to deal with EMI and EMC for industries such as telecom equipment manufacturing or automotive industry <sup>[25] [26]</sup>. All properly designed and tested electronic products (commercial or industrial) are tested for EMI/EMC by professional compliance test facility like UL prior to release in the large scale mass market <sup>[21] [22]</sup>.

On a different note, every signals will face attenuation no matter the medium they are passing through. In case of electronics, the medium is generally copper which is a very good conductor of electricity. Even though copper is a very good conductor of electricity, it has certain amount of resistivity i.e. resistance. The resistance will cause the signal to get attenuated. Given that the signal travels a distance long enough, it could be attenuated such that the digital HIGH of 2.4v (considering 5v TTL [9]) may drop to unaccepted (metastable) region which will most definitely cause signal error in the receiver. Attenuation is applicable for both signal and power distribution. This is the reason why all professional PCB CAD packages has a dedicated Power Integrity Analysis and Signal Integrity Analysis e.g. leading IC design package from Cadence has a dedicated tool for Signal and Power integrity analysis called 'Sigrity'.

By combining all of the above stated real life impeding conditions and applying it to Parallel Data BUS, from engineering perspective, it can be observed that if transmission distance is too long there is a possibility that the data will be attenuated too much and/or distorted by noise or EMI/EMC. From financial point of view, carrying a large number of wires over extended distance is costly and wasteful. In such situations it is convenient to transfer data in series. Serial transmission(s) requires fewer number of wires compared to parallel communication and data can be transmitted across long distance using proper transmission protocols like differential pairing. This makes serial transmission cheaper and more convenient from engineering point of view and economical from financial point of view.

A very brief comparison of Serial versus Parallel communication BUS is depicted on table 2.1.

| <u>Attributes</u>           | Name of data BUS                                                                                                                                  |                                                                                                                |  |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|

|                             | Serial                                                                                                                                            | Parallel                                                                                                       |  |

| Number of<br>Physical wires | 1 wire can carry multiple bits and so,<br>the number of wires can be drastically<br>reduced                                                       | Multiple wires, 1 wire per bit data                                                                            |  |

| EMI generation              | Higher than Parallel BUS (as operating frequency is higher)                                                                                       | Relatively lower than Serial BUS                                                                               |  |

| EMI reduction               | EMI can be suppressed using differential signal and using properly terminated shielded cables                                                     | Wires can be shielded to decrease EMI emission                                                                 |  |

| Noise<br>susceptibility     | High if proper shielded cable and/or differential signaling is not used                                                                           | Wires can be shielded to increase noise susceptibility                                                         |  |

| Bit rate                    | Clock has to be much faster to be same rate as parallel counterpart                                                                               | Single clock can transmit<br>multiple bits, therefore orders of<br>magnitude faster than serial<br>counterpart |  |

| Latency                     | High                                                                                                                                              | Significantly lower than Serial counterpart                                                                    |  |

| Range                       | High, in the range of Km using differential signaling                                                                                             | Low, large distance parallel cable is possible but impractical                                                 |  |

| Cost                        | Much lower than parallel, only practical way to carry data through wired medium  Impractical, incurs high c cable, maintenance ar troubleshooting |                                                                                                                |  |

Table 2.2 Comparison between Serial and Parallel BUS

## Chapter - 3

## Common protocols for 8-bit serial communication

This section briefly explains the working principle and usage of two most commonly used serial data communication protocols. Both of these protocols are industry standard and are used in numerous industrial, commercial and consumer electronics. Please note that only the serial communication protocols that uses up to two physical wires for data exchange are discussed in this chapter. The brief explanation of these serial communication protocols will later be used to justify the need for a single wire communication BUS.

#### 3.1 I2C/IIC [17]

Invented in the late 1980's by Philips Semiconductor (now NXP), IIC is an 8-bit data communication BUS that allows multiple embedded systems, SOC or MCU to communicate between each other. IIC is the original name that was given by Philips, however, other corporations such as Atmel (now Microchip Technology Inc.) uses the license from NXP to use IIC with their own products while renaming IIC to TWI [19] (TWI is specific branding of Microchip Technology Inc.). IIC (also known as I2C and I<sup>2</sup>C) stands for Inter Integrated Circuit. Two Wire Interface (TWI) is the name given by Atmel/Microchip to avoid violating NXP's trademark but apart from name both are same in all aspects. IIC is a half-duplex, low speed, synchronous data BUS. Presently, this protocol for communication is widely used by system engineers and hardware developers to glue down several embedded systems together. Its wide use in industry has forced a common industry standard to be created. IIC is used in modern systems like voltage regulator and Clock generator chip on computer, displays on lab instruments, HDMI port for monitors and on active probes for oscilloscope etc.

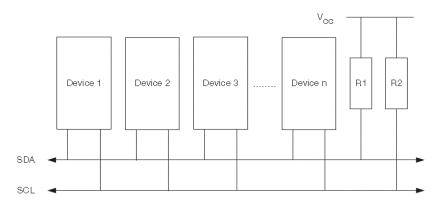

The basic advantage of IIC is that it requires only two wires for bidirectional transmission namely SCL & SDA [17]. SCL is system clock and SDA is system data. As a system clock is involved, it is a synchronous system. Two wire IIC works great except for its limitation that the capacitance between SCL & SDA, relative to ground, must be less than 400pf (may depend on the chip

generating CLK). Therefore, IIC is not suitable for long distance communication through wire (buffers are available to increase range to some extent). The clock frequency is user defined. Higher the clock frequency, the greater is the capacitance between SCL & SDA and with respect to ground. Thus a middle ground between range and speed needs to be established during the BUS implementation.

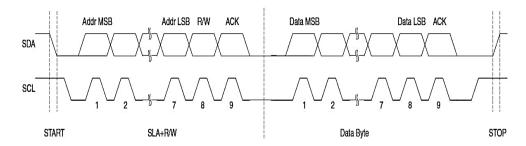

#### 3.2 Working principel of IIC [13] [17] [19]

All IIC compatible devices must be connected in parallel to each other as daisy chain. The SCL and SDA of all compatible devices must be connected to the SCL and SDA of the BUS respectively. The IIC works in Master Slave fashion. At any time, there can be several Slaves but only one Master. Each Slave is assigned a unique address. As IIC is 8-bit data BUS and has 7-bit address, maximum 127 devices (address of 0x00 is reserved as General call) can be connected to it at a time. The Master device is responsible for generating the clock signal and all of the control signals. When the Master device needs to communicate with any of the Slave device, it generates START condition, places the 7-bit/10-bit (depends on manufactures) slave address along with 1-bit read/write bit. If the Slave returns ACK, the Master reads or writes from/to the Slave. If MASTER doesn't need to use the BUS anymore, it generates STOP condition. If the Master needs to use the BUS but don't want to release the BUS, it generates REPEATED START condition. START & STOP can be generated only once but REPEATED START can be generated as many times as needed.

Sometimes there may be multiple Master in the system. At any time only one Master can control the BUS. During that time all other devices are treated as Slave. If multiple Master tries to take control of the BUS at the same time, the condition is called ARBRITRATION. If ARBRITRATION arises, the BUS becomes first come first serve (procedure must be present in algorithm to handle ARBRITRATION). The Master that reached first takes control of the BUS and the other Master(s) revert back to Slave status and wait for the BUS to be free up.

Figure 3.1 IIC timing diagram for sending Address followed by data [19]

IIC uses the classic open drain configuration. Therefore, in order to use IIC, both the SCL and SDA pins of the MCU must be physically pulled up by the user. Pulling up can be done via single resistor on each IC pins. The value of the pull up resistor depends the BUS speed and BUS length. This is to be done as IIC can only pull down and can't pull up as IIC has an internal open drain connection. Therefore, any break in the pull up circuit will make the whole system unstable as IIC is used as the central data BUS. Only one pull up circuit is enough for a whole system.

Figure 3.2 Devices and pull-up resistor connection of a typical IIC BUS [19]

Pulling up is conventionally done on the slave side. The resistors used for pulling up are determined by the speed of the BUS. The resistance can range from 1K to 10k. The theoretical value of resistance can be calculated from the specification formula. A good rule of thumb is to use 4.7 K $\Omega$ . It should be noted that both resistors must be of same value and with very tight tolerance and temperature coefficient.

Complete IIC user manual is presented in the reference [17].

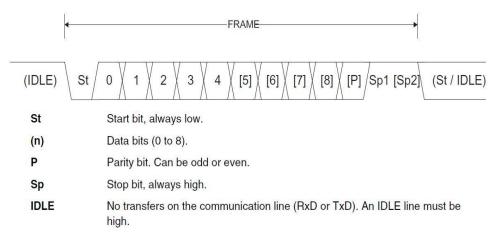

#### 3.3 Serial Protocol (EIA/TIA 232) [1] [4] [7]

The most commonly used serial I/O standard for computers and electronic instrumentations is TIA/EIA-232 which is most commonly known as RS232. Serial protocol for MCU can be either USART or UART. USART stands for Universal Synchronous Asynchronous Receiver Transmitter. UART stands for Universal Asynchronous Receiver Transmitter. USART means data can be transferred both synchronously and asynchronously while UART is asynchronous communication only. The data is received by another device with RS232 standard serial port. In synchronous mode, one character or one 8-bit block of data is send at a time. In asynchronous mode, a whole byte is send. If synchronous mode is used, another physical wire must be used to send Clock signal making total number of wires three.

Serial protocol has three different standards namely RS232, RS422 and RS485. These standards were set by Electronics Industries Association (EIA) to maintain communication compatibility among devices made by different manufactures. It is today most widely used I/O interfacing standard used in PC, industrial and lab equipment and in other electronics where serial communication is needed. The USB port that we frequently use on computer is actually a RS232 port with a USB to Serial converter.

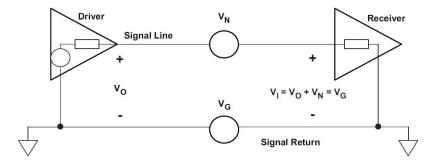

It should be noted that these standards were set in the 1960s and updated for newer technology on the 1980s. Digital technology was still at its infancy on 1960s. That was the era of analog electronics. These standards were set to entertain the 1960s standards and requirements. Only RS232 is used on MCU as RS422 and RS485 requires differential signaling leaving only RS232 as single ended. Figure 3.3 and 4.3 shows both single ended and differential signaling respectively.

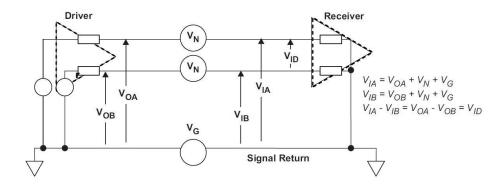

Figure 3.3 Single ended transmission with line noise and ground noise model [1]

Figure 3.4 Differential transmission with line noise and ground noise model [1]

Differential pairs are capable of conveying signals a much longer distance than its single ended counterpart. A differential pair transmits the same signal via two closely placed parallel physical wires. One of the wires carries the actual signal and the other one carries the inverted image of the original. The parallel wires are close enough to form capacitive coupling to each other. This setup allows a very high immunity to noise/EMI and attention which effectively increases the range of the BUS. Modern microcontrollers generally have serial protocol using TIA/EIA-232 single ended form. If differential signaling is required, external circuitry needs to be added.

In TIA/EIA232 standard, digital HIGH (1) is represented by -3v to -15v and digital LOW (0) by +3v to +15v. The gap of -3v to +3v is undefined. To convert it to today's TTL standard, a converter needs to be used. Maxim/Dallas MAX232 is such a converter. It is bidirectional and can be used to both receive and transmit. In RS232 there is one pin RX for receiving and one pin TX for transmitting along with other control and status pins however only TX and RX pins can be used to communicate between devices with very little error. If VCC and GND are considered, a total of four wires are needed for complete asynchronous bidirectional serial transmission.

Figure 3.5 shows the data frame format of TIA/EIA 232.

Figure 3.5 Data frame format of TIA/EIA 232 standard [19]

#### 3.4 Requirement for single wire BUS

A common problem often faced by hardware developers is the fact that the numbers of physical I/O pins on the microcontroller may run out before the task at hand is completed. Modern microcontrollers are designed with a large number of features built into a chip of relatively small physical footprint. To ensure all features can easily be accessed while minimizing the physical footprint of the microcontroller, a single I/O pin may be used to serve more than one function. Thus it is very easy to have high pin usage count in the applications that uses a lot of the microcontroller's features. In this type of situation, it is often wasteful to dedicate multiple I/O pins for whatever serial communication protocol that is being used. Also often times the application demands that data is exchanged between multiple different types of standalone embedded systems with possibility of hot swap option. Removing system(s) from a data BUS without some sort of notification can crash the larger embedded system.

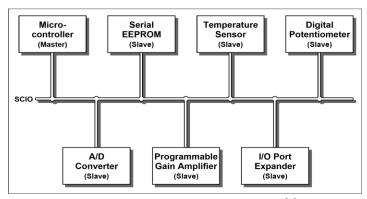

A bidirectional data BUS using only one I/O pin can reduce wastage of I/O pins while facilitate addition of standalone application chips such as EEPROM, ADC, Port expander, LCD display driver, PWM controller etc. Situations demanding minimum number of physical wires for bidirectional data exchange, single wire data BUS are without rival.

A brief comparison between IIC and RS-232 standard in presented in table 3.1.

| Attributes           | Name of Data BUS                                               |                                                                                                                                        |  |

|----------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

|                      | IIC                                                            | TIA/EIA 232 *1                                                                                                                         |  |

| Number of wires      | 2                                                              | <ul><li>2 for asynchronous</li><li>3 for synchronous</li></ul>                                                                         |  |

| BUS Protocol         | Defined as common industry standard                            | RS-232 (industry standard)                                                                                                             |  |

| Clock Speed          | 100 to 400 KHz typical<br>1000 KHz maximum                     | 2400 KHz minimum<br>115 KHz maximum (typical)                                                                                          |  |

| Signal type          | Digital                                                        | <ul> <li>Designed for Analog communication systems</li> <li>Can be converted to modern digital standard by using converters</li> </ul> |  |

| BUS type             | Serial                                                         | Serial                                                                                                                                 |  |

| Signaling            | Single ended only                                              | RS232 – Single ended<br>RS 422 – Differential *2<br>RS 485 – Differential *2                                                           |  |

| Range                | Wire length is restricted by line capacitance of maximum 400pf | RS 232 – 20m<br>RS 422 – 1200m *2<br>RS 485 – 1200m *2                                                                                 |  |

| BUS direction        | Half duplex                                                    | Full duplex                                                                                                                            |  |

| Device configuration | Master Slave system                                            | TX and RX can operate independently (RS 422 & RS 485 are Multidrop)                                                                    |  |

Table 3.1 comparison between IIC and TIA/EIA 232

#### Notes:

<sup>\*1.</sup> Assume the RS-232 standard for embedded systems. Some devices have built in UART modules that require 3 pins for synchronous communication e.g. Atmega32A MCU.

<sup>\*2.</sup> Different standard, presented here for reference and comparison purpose only.

## Chapter – 4

## **Existing single wire BUS protocols**

Presently multiple single wire BUS protocols exist in the market. These protocols are widely used in commercial products where absolutely minimum number of wires are needed to implement low speed BUS carrying non critical data. All of these single wire BUS are patented/copyrighted and use their own protocol for data transmission and signal generation. Two most popular ones are 1-Wire protocol form Maxim Integrated and UNI/O from Microchip Technology Inc. Both of these BUS are explained briefly in this section.

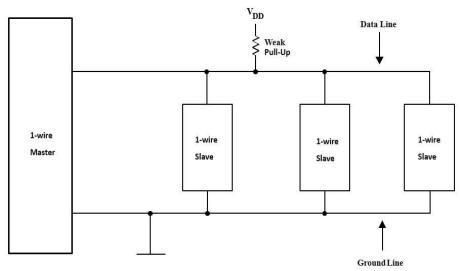

#### **4.1 1-Wire Protocol** [12] [14]

Maxim Integrated owns a proprietary single wire BUS that is currently being used widely in commercial applications. Maxim 1-Wire Protocol was initially designed to form a data BUS that can communicate between one Master and multiple slaves sharing the same data BUS located on a PCB. As the usage of devices using 1-Wire protocol increased, Maxim Integrated found a way to extend the range of 1-Wire protocol beyond the PCB and converted the BUS into a network which has been named MIcroLAN. Present application of 1-Wire protocol includes but not limited to accessories, clone prevention, peripherals, security feature, intellectual property protection, PCB identification and authentication etc. [28].

1-Wire protocol utilizes Master-Slave configuration. The Master device is responsible for generating the required waveforms. 1-wire protocol is designed to be used in low speed embedded systems. The BUS or network uses open drain environment i.e. to use the BUS or network, a resistor must be used to pull-up the BUS to VCC. The value of the pull-up resistor depends on the BUS length, network topology, data rate or device power source [14].

One of the most interesting feature of 1-Wire Protocol is Parasitic Power which means that the Master device is able to provide the slave device power through the BUS itself. This feature allows 1-Wire Protocol to operate using only two physical wire namely BUS and GND. Therefore, the slave device can be designed to have no external power supply (not even battery) which makes the resulting product to have a very small physical dimension. However, this feature also impacts the BUS speed and thereby reduces data transfer bit rate.

Figure 4.1 Typical device connections of 1-wire protocol [12]

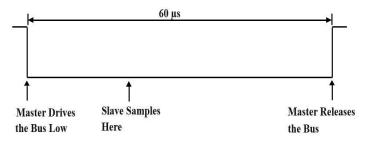

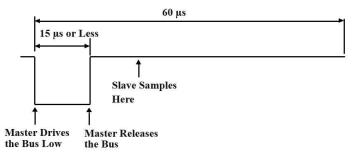

Bit definition on 1-Wire is done by pulling down the BUS for specific time. 1-Wire has 4 different operations namely

- Write '1' bit

- Write '0' bit

- Read

- Reset

Each of these operations are implemented using different amount of delay to pull down the BUS. The following table 4.1 shows the operations and the conditions to implement these operations.

| Operation         | Description                                                            | Implementation                                                                                                                                                                                                                                                   |

|-------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read ( any bit)   | Read 1 bit from slaves                                                 | <ol> <li>Drive BUS low for 6 μs</li> <li>Keep BUS released for 9 μs</li> <li>Sample BUS for next 55 μs to receive one bit from slave</li> </ol>                                                                                                                  |

| Write ( '0' bit ) | Write (send) '0' bit to the slaves                                     | <ol> <li>Drive bus low for 60 μs</li> <li>Keep BUS released for 10 μs</li> </ol>                                                                                                                                                                                 |

| Write ( '1' bit)  | Write (send) '1' bit to the slaves                                     | <ol> <li>Drive BUS low for 6 μs</li> <li>Keep BUS released for 64 us</li> </ol>                                                                                                                                                                                  |

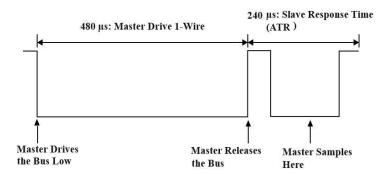

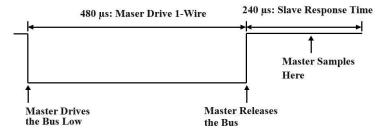

| Reset             | Reset all 1-wire slave devices and get them ready to receive a command | <ol> <li>Drive BUS low for 480 μs         Keep BUS released for 70         μs</li> <li>Sample BUS for next 410         μs to receive ATR</li> <li>'0' = at least on slave         device is present</li> <li>'1' = no slave device is         present</li> </ol> |

Table 4.1 Commands and their respective implementation timing for 1-wire protocol [12] [16]

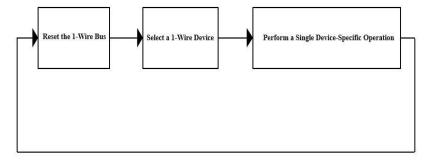

Figure 4.2 Typical communication flow of 1-wire protocol [12]

Timing diagram of 1-Wire is as follows for all of 1-wire protocol operations [12].

Figure 4.3 1-wire protocol **Reset** with at least 1 slave

Figure 4.4 1-wire **Reset** with no slave

Figure 4.5 1-wire Write 0 (digital LOW)

Figure 4.6 1-wire Write 1 (digital HIGH)

Figure 4.7 1-wire **Read 1** (digital HIGH)

Figure 4.8 1-wire **Read 0** (digital LOW)

With all of these operations being setup perfectly, the 1-Wire can operate at two different bit rates of

- Standard at 16.3 Kbit/s [12] [16]

- Overdrive at approx. 110 Kbit/s [12] [16]

Complete details of 1-Wire can be accessed from the reference [12] [14] & [16].

#### 4.2 UNI/O [2]

UNI/O is the single wire BUS designed, owned and patented by Microchip Technologies Inc. This is also a low speed BUS developed to carry data to multiple devices/components while using as small number of physical connections as possible to carry the data. UNI/O uses one I/O pin to communicate with all connected devices. Typical application of UNI/O of UNI/O includes but not limited to ADC, EEPROM, I/O Port Expander and wide range of sensors <sup>[2]</sup>.

Figure 4.9 UNI/O BUS example [2]

UNI/O also uses Master-Slave configuration to communicate. The Master is responsible for determining the clock period, generating the data signals, controlling the BUS access and initiate all operations and modes. Both Master and Slave can be configured as transmitter and receiver however, Master is responsible for determining the active mode.

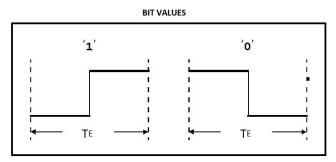

Both the clock and data is encoded together using Manchester Encoding. In Manchester encoding, each data bit is transmitted within a specified bit period. The bit period is defined by the Master at the starting of the communication. The bit period is sent to the Slave device by the Master device by transmitting a value of 0x55 (0b01010101) at the start header of the command. Each bit period includes an edge transition in the middle. The direction of the edge transition determines the logical state of the bit. A rising edge signifies a logical HIGH and a falling edge signifies a logical LOW.

Figure 4.10 Manchester encoding [2]

Figure 4.11 UNI/O one-byte transmission using Manchester Encoding [2]

When Master needs to communicate with any of the Slaves, it selects the Slave by transmitting 8-bit or 12-bit address. After transmission of device address, the Master must send a command byte to declare its intended operation. The types of operations are predefined on the devices. A complete operation can consist of a single byte to theoretically infinite number of bytes. Acknowledge and Not-Acknowledge bits are transmitted by both Master and Slave where they are needed. Acknowledgement bytes are named as follows

- MAK Master Acknowledge

- NoMAK Master Not Acknowledge

- SAK Slave Acknowledge

- NoSAK Slave Not Acknowledge

Figure 4.12 UNI/O complete one-byte transmission with both Master and Slave Acknowledgement [2]

A full operation always consists of the following steps

- Standby Pulse

- Start Header

- Device Address

- Command Byte

- Other necessary bytes required for the operation

Figure 4.13 Complete timing diagram for read operation from UNI/O compatible EEPROM [2]

A complete BUS specification for the UNI/O can be accessed from the reference [2].

# Chapter – 5

# **Proposed Single Wire BUS**

Although low speed single wire data BUS for embedded systems exist in the market and are used widely in commercial and industrial applications, they use either delay in the signal or Manchester encoding for logical bit definition. The motivation of this research is to find another way multiplex both clock and data and send them down the same physical wire while making an attempt to have a higher communication bit rate than that are offered by standard transmission rate of the existing protocols. Attempts are to be made to keep the hardware for the BUS as simple as possible so that it can be simulated in real life with ease and, if commercially available, can be produced with a low cost. With all these requirements in mind, the specifications for the proposed single wire data BUS is defined as follows

- One Wire deployment

- Synchronous

- Half duplex

- Carries 8-bit data with 2-bit command header at 10-bit total

- Master-Slave configuration

- ACK/NACK/BUSY status transmission by both Master and Slave

- Data rate of 15 Kbits/sec

- Communication range is within the PCB only i.e. short distance

- Single ended signaling

## 5.1 Working principle

The biggest problem of sending data and clock together through a single wire is to differentiate between the data and clock at the receiver (discussed more at the concluding chapter). Algorithm can be generated to sample the data BUS at specific intervals until specific number of samples are taken and then based on predefined rules, clock and data is separated. However, this approach

beats the idea of a synchronous BUS as the samples are taken at specific interval rather than on arrival of a clock signal. As the sampling circuit is not triggered by an external clock signal, there is no point in sending a clock signal mixed with data bits to begin with. Also this approach runs the risk of inaccurately labeling the clock signal as data and vice versa in case there is any mismatch in timing between sending of the data and sampling it. The aforementioned single wire protocols address these problems by either

- using Manchester encoding on UNI/O from Microchip Technology Inc. [2]

- holding the line down for specific delay and synchronizing the data on falling edge of the signal on 1-Wire protocol from Maxim Integrated [12]

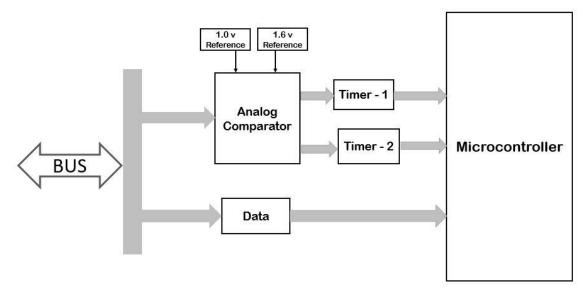

The proposed data BUS multiplexes the clock and data for transmission using same physical wire by assigning different voltage levels for data and clock. The conventional 5v TTL standard is slightly modified to suit this purpose. In the conventional setup, any signal with voltage level of greater than or equal to 2.4v is regarded as digital HIGH (logical 1) and signals with voltage levels less than or equal to 0.4v is regarded as digital LOW (logical 0). The mid-section between HIGH and LOW (from 0.4v to 2.4v), there is an unacceptable region. According to the 5v TTL standard, signals with voltage in this region is neither 1 nor 0 and is regarded as unacceptable. In the proposed BUS, while data signal is assigned the common 5v TTL standard for logical 1 (HIGH) and 0 (LOW), clock is assigned a voltage value midway between HIGH threshold and LOW threshold. The middle section of HIGH threshold and LOW threshold is unaccepted (metastable) region and is not used by the TTL standard. The clock signal is assigned a small region of 600mV inside the unaccepted 2.0v region. The region for clock signal starts at 1.0v and continues up to 1.6v. Figure 5.1 shows the conventional 5vTTL standard and the modified TTL standard for the proposed BUS.

Figure 5.1 Voltage Levels for the logic states

(a) Conventional 5v TTL standard [9], (b) Modified standard for the proposed single wire BUS

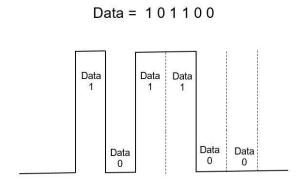

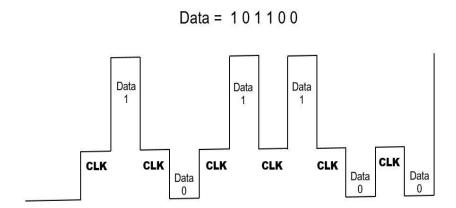

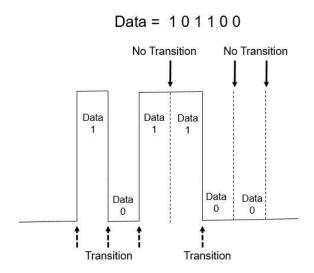

The waveform for digital signal using conventional 5v TTL standard is shown in figure 5.2. In this case a 6-bit number of 0b101100 is being sent.

Figure 5.2 Digital signal waveform for conventional TTL standard

The same 6-bit number of 0b101100 when sent by the proposed modified TTL standard will assume the shape shown in figure 5.3. The clock signal and data signals are send in sequentially. Therefore, there is always a data signal next to the clock signal. Clock signal comes first followed by the data bit. The clock signal signifies the start of a new data bit. The receiver gets itself ready for receiving 1-bit data on arrival of a clock signal.

Figure 5.3 Digital signal waveform for proposed single wire standard

The transmitter is connected to the signal multiplexer and the receiver is connected to the isolator and data buffer (explained in detail in the next chapter). Both signal multiplexer and isolator consists of multiple blocks, each performing different functions. Throughout this whole literature, circuit that combines CLK and digital data is referred to as multiplexer and circuit that separates CLK and digital data from the multiplexed signal is referred to as isolator. Both the signal multiplexer and isolator has one physical connection to the data BUS, however, there are multiple physical wire connections between the signal multiplexer, isolator and the transmitter and receiver respectively. Both transmitter and receiver shares a common ground voltage reference (GND). The signals going into and out of the multiplexer and demultiplexer respectively are omnidirectional.

The multiplexing circuit is designed to have two stages, one for generating clock signals (1.0v to 1.6v) and another to generate data signals (less than 0.5v or greater than 2.3v). The multiplexing circuit has two inputs for driving it. The transmitter is responsible for generating the ON/OFF pattern for the different encoder blocks based on the given data to be transmitted. The output of clock driver and Data driver connects directly to the BUS.

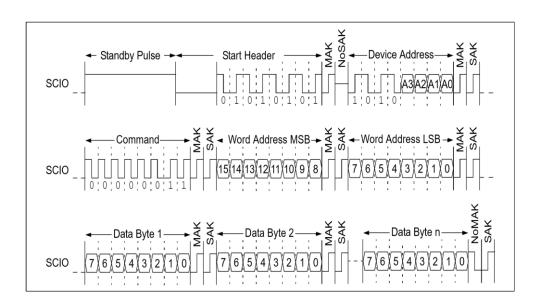

## 5.2 Data frame format, BUS modes and communication protocol

As this thesis research is dealing with a non-existent data BUS, the complete communication protocol must be built from scratch in order to make the data BUS communicate during the real

life hardware emulation. This section sets the outline for the communication protocol, frame format and different modes used by the BUS to configure and/or communicate data between multiple standalone devices. Complete protocol will be generated in the next chapter(s) where the physical hardware is developed and simulated.

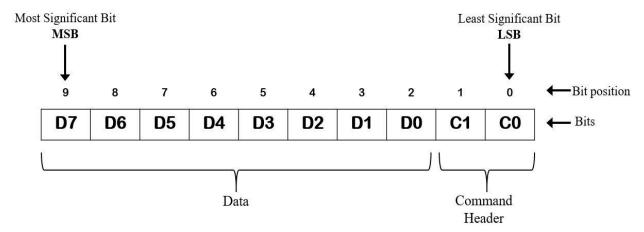

#### **5.2.1 Data frame format**

The proposed BUS communicates by sending/receiving data packet of predefined length. Data packet for the proposed BUS is defined in the research to be 10-bit long. The least two significant bits are the command headers and the rest 8-bits are the data. The most significant bit of data is also the most significant bit of the packet. That makes the least significant bit of data the 2<sup>nd</sup> bit of the packet. Data frame format for the proposed BUS is shown in figure 5.4.

Figure 5.4 Data frame for the proposed single wire standard

#### 5.2.2 BUS modes

The proposed data BUS has two different modes namely setup mode and general mode. During setup mode, all communicated data is used to configure the devices attached to the BUS. During general mode or general purpose mode, all communicated data are considered to be common traffic that will in no way modify any of the device configuration. All data communicated during general mode are directly conveyed to the user. Refer to table 5.1 for complete description of command

header combinations. Most of the combination in the command header are not used in this research and is reserved for future development.

|         | Bits       |    |                                   |  |

|---------|------------|----|-----------------------------------|--|

| Mode    | <b>C</b> 1 | C0 | Description                       |  |

|         | 0          | 0  | Unused                            |  |

| Setup   | 0          | 1  | Initialization of a slave         |  |

|         | 1          | 0  | Unused                            |  |

|         | 1          | 1  | Unused                            |  |

|         | 0          | 0  | Unused                            |  |

| General | 0          | 1  | Master intends to Read from slave |  |

|         | 1          | 0  | Unused                            |  |

|         | 1          | 1  | Master intends to write to slave  |  |

Table 5.1 Command headers and their respective mode descriptions

## **5.2.3 Communication protocol**

The proposed BUS is designed to have a single master and multiple slaves at a time. The address is of 8 bits and therefore, theoretically, there can be maximum of 256 ( $2^8 = 256$ ) devices on the BUS at a time including master and slaves. As the BUS is designed to have only one master, maximum of 255 slave devices can be controlled by one master. The master device possesses complete control of the BUS. The master can communicate with any slave it wants but the slaves cannot communicate between themselves. The slave device cannot even communicate with the master unless it has been specifically instructed to do so by the master.

As stated earlier, the BUS has two different modes and a data packet size of 10 bits and two different modes of operation with which it can communicate with the slave device. All this aforementioned information is compiled together to form a complete functional single wire data

BUS. The complete protocol for errorless communication of data between a master device and a slave device is stated on section 5.5.

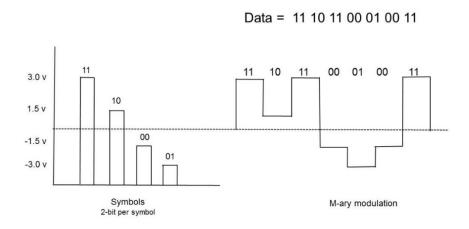

## 5.3 M-Ary signaling and buffering

One can raise the argument that the signal shape of the proposed single wire BUS resembles that of the M-ary modulation method widely used in the telecommunication industry. However, that is far from the truth. M-Ary modulation consists of multiple symbols each symbol specified by a specific voltage level. Each symbol represents a certain combination of binary numbers. In the proposed BUS, the voltage levels represent either digital HIGH/LOW or a CLK signal. Figure 5.3 shows the example of a m-ary modulation of 14-bit binary data of 11101100010011. Each symbol in figure 5.3 represents a specific 2-bit combination.

Figure 5.5 M-ary modulation of binary data [19]

M-ary modulation becomes increasingly susceptible to noise as the number of combinations per symbol increases. However, theoretically speaking, the proposed BUS will have a higher susceptibility to noise, relative to M-ary modulation. The receiver or buffer/repeater will know specifically which signal it is amplifying. After a CLK signal, there will only be room for a digital signal. After the digital signal, only expectation is CLK signal. Therefore, it is virtually impossible for the receiver or buffer/repeater to mix-up between CLK and data and amplify the wrong type. The buffer/repeater will have to have two separate stages. One will reinforce digital signals and other the CLK signal. It will need some control system to determine the correct stage and switch

between two stages. The buffer/repeater need not be a single standalone system as it can be embedded on the receiver. This research will not be going forward with designing buffer/repeater.

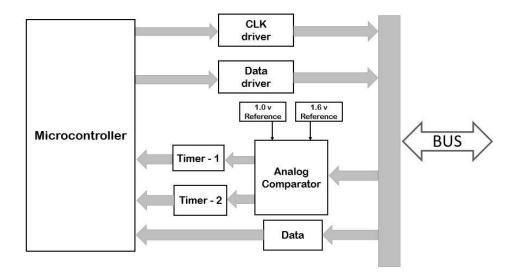

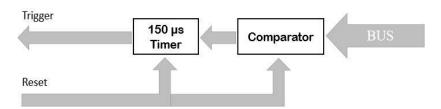

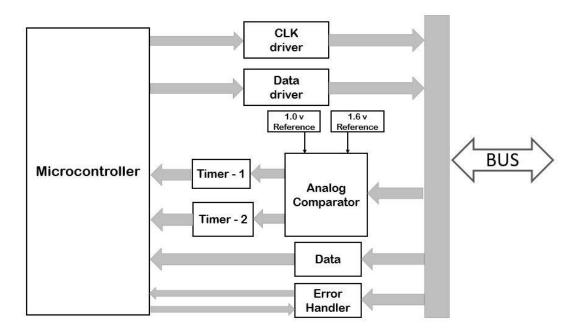

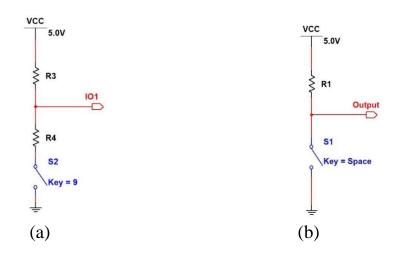

## 5.4 System and sub-system block diagrams